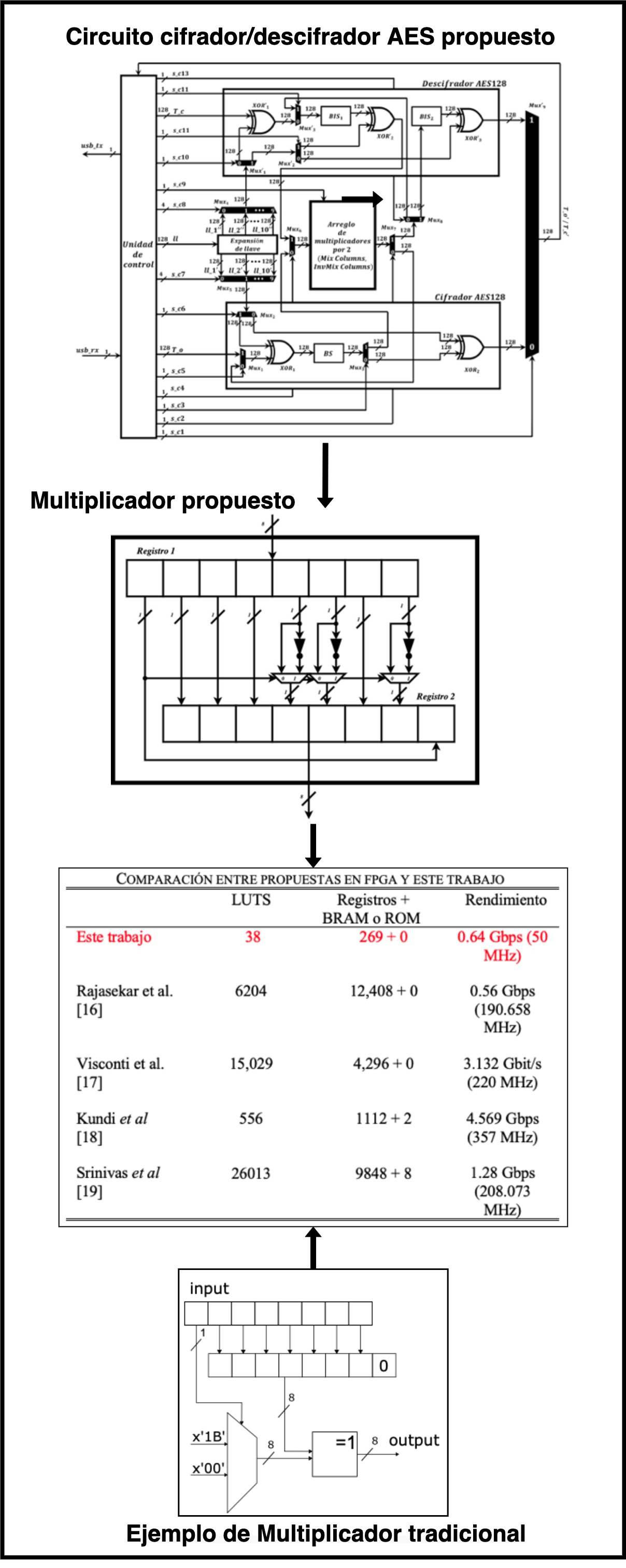

A low-cost and highly compact FPGA-based encryption/decryption architecture for AES algorithm

Keywords:

FPGA, AES, Advanced Encryption Standard algorithm,, encryptor / decryptor, GF (2^8) multiplierAbstract

Nowadays, the design of ultra-compact area advanced encryption standard (AES) architectures is highly demanded by the electronics industry since many of these architectures are embedded in portable devices, such as smart phones, tablets, etc., in which the area is critically limited. Until now, many approaches have been proposed to create high-processing and compact architectures. However, the area consumption is still a factor to be improved. In this paper, a highly compact encryption/decryption architecture, which is implemented in a low-cost FPGA, to efficiently simulate the AES algorithm, is proposed. Specifically, an optimized Galois Field Multiplier, which is the most demanding operation in terms of area consumption and processing speed, involved in Mix-Columns and Inverse Mix-Columns transformations, is presented. Therefore, the optimization of the proposed GF (2^8) multiplier by two has allowed to us create an ultra-compact Mix-Columns circuit since this circuit involves large number of multiplications. In addition, the design involves a routing circuit which allowed the proposed architecture to perform encryption or decryption by using common modules. The results demonstrate that the proposed digital circuit expends fewer LUTs and fewer registers when compared with the most compact encryption/decryption architectures reported to date.

Downloads

References

M. A. Jan, F. Khan, M. Alam, y M. Usman, “A payload-based mutual authentication scheme for Internet of Things,” Future Generation Computer Systems, vol. 92, pp. 1028–1039, Mar. 2019, doi: 10.1016/j.future.2017.08.035.

D. Bui, D. Puschini, S. Bacles-Min, E. Beigné y X. Tran, "AES Datapath Optimization Strategies for Low-Power Low-Energy Multisecurity-Level Internet-of-Things Applications," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 12, pp. 3281-3290, Dec. 2017, doi: 10.1109/TVLSI.2017.2716386.

U. Farooq y M. F. Aslam, “Comparative analysis of different AES implementation techniques for efficient resource usage and better performance of an FPGA”, Journal of King Saud University - Computer and Information Sciences, vol. 29, núm. 3, pp. 295–302, jul. 2017, doi: 10.1016/j.jksuci.2016.01.004.

E. A. Hernandez Diaz, H. M. Perez Meana, y V. M. Silva Garcia, “Encryption of RGB Images by Means of a Novel Cryptosystem using Elliptic Curves and Chaos”, IEEE Latin America Transactions, vol. 18, núm. 08, pp. 1407–1415, ago. 2020, doi: 10.1109/TLA.2020.9111676.

J. L. Corchuelo y S. J. Rueda, "AndroidBLP for Confidentiality Management in Android Environments," in IEEE Latin America Transactions, vol. 15, no. 3, pp. 496-502, March 2017, doi: 10.1109/TLA.2017.7867600.

M. Khan y N. Munir, “A Novel Image Encryption Technique Based on Generalized Advanced Encryption Standard Based on Field of Any Characteristic”, Wireless Personal Communications, vol. 109, núm. 2, pp. 849–867, nov. 2019, doi: 10.1007/s11277-019-06594-6.

A. Soltani y S. Sharifian, “An ultra-high throughput and fully pipelined implementation of AES algorithm on FPGA”, Microprocessors and Microsystems, vol. 39, núm. 7, pp. 480–493, oct. 2015.

S. S. Priya, P. Karthigaikumar, N. M. Siva Mangai, y P. Kirti Gaurav Das, “An Efficient Hardware Architecture for High Throughput AES Encryptor Using MUX Based Sub Pipelined S-Box”, Wireless Personal Communications, vol. 94, núm. 4, pp. 2259–2273, jun. 2017, doi: 10.1007/s11277-016-3385-7.

V. K. Sharma, S. Kumar, y K. K. Mahapatra, “Iterative and Fully Pipelined High Throughput Efficient Architectures of AES in FPGA and ASIC”, Journal of Circuits, Systems and Computers, vol. 25, núm. 05, p. 1650049, may 2016, doi: 10.1142/S0218126616500493.

R. R. Farashahi, B. Rashidi, y S. M. Sayedi, “FPGA based fast and high-throughput 2-slow retiming 128-bit AES encryption algorithm”, Microelectronics Journal, vol. 45, núm. 8, pp. 1014–1025, ago. 2014.

H. Lee, Y. Paik, J. Jun, Y. Han, y S. W. Kim, “High-throughput low-area design of AES using constant binary matrix-vector multiplication”, Microprocessors and Microsystems, vol. 47, pp. 360–368, nov. 2016, doi: 10.1016/j.micpro.2016.10.003.

V. Nandan y R. Gowri Shankar Rao, “Minimization of digital logic gates and ultra-low power AES encryption core in 180CMOS technology”, Microprocessors and Microsystems, vol. 74, p. 103000, abr. 2020, doi: 10.1016/j.micpro.2020.103000.

S. Shanthi Rekha y P. Saravanan, “Low-Cost AES-128 Implementation for Edge Devices in IoT Applications”, Journal of Circuits, Systems and Computers, vol. 28, núm. 04, p. 1950062, abr. 2019, doi: 10.1142/S0218126619500622.

Advanced Encryption Standard, FIPS 197, National Institute of Standards and Technology, nov. 2001.

R. Ueno et al., "High Throughput/Gate AES Hardware Architectures Based on Datapath Compression," in IEEE Transactions on Computers, vol. 69, no. 4, pp. 534-548, 1 April 2020, doi: 10.1109/TC.2019.2957355.

P. Rajasekar y H. Mangalam, “Design and implementation of power and area optimized AES architecture on FPGA for IoT application”, Circuit World, vol. ahead-of-print, núm. ahead-of-print, jun. 2020, doi: 10.1108/CW-04-2019-0039.

P. Visconti, S. Capoccia, E. Venere, R. Velázquez, y R. de Fazio, “10 Clock-Periods Pipelined Implementation of AES-128 Encryption-Decryption Algorithm up to 28 Gbit/s Real Throughput by Xilinx Zynq UltraScale + MPSoC ZCU102 Platform”, Electronics, vol. 9, núm. 10, p. 1665, oct. 2020, doi: 10.3390/electronics9101665.

D.-S. Kundi, A. Aziz, y N. Ikram, “A high performance ST-Box based unified AES encryption/decryption architecture on FPGA”, Microprocessors and Microsystems, vol. 41, pp. 37–46, mar. 2016.

N. S. S. Srinivas y Md. Akramuddin, “FPGA based hardware implementation of AES Rijndael algorithm for Encryption and Decryption”, en 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT), Chennai, India, mar. 2016, pp. 1769–1776.

J. Daemen y V. Rijmen, Specification for the Advanced Encryption Standard (AES). Federal Information Processing Standards Publication 197, 2001.

DE0-CV User Manual, Terasic Inc., Hsinchu City, Taiwan, 2016.