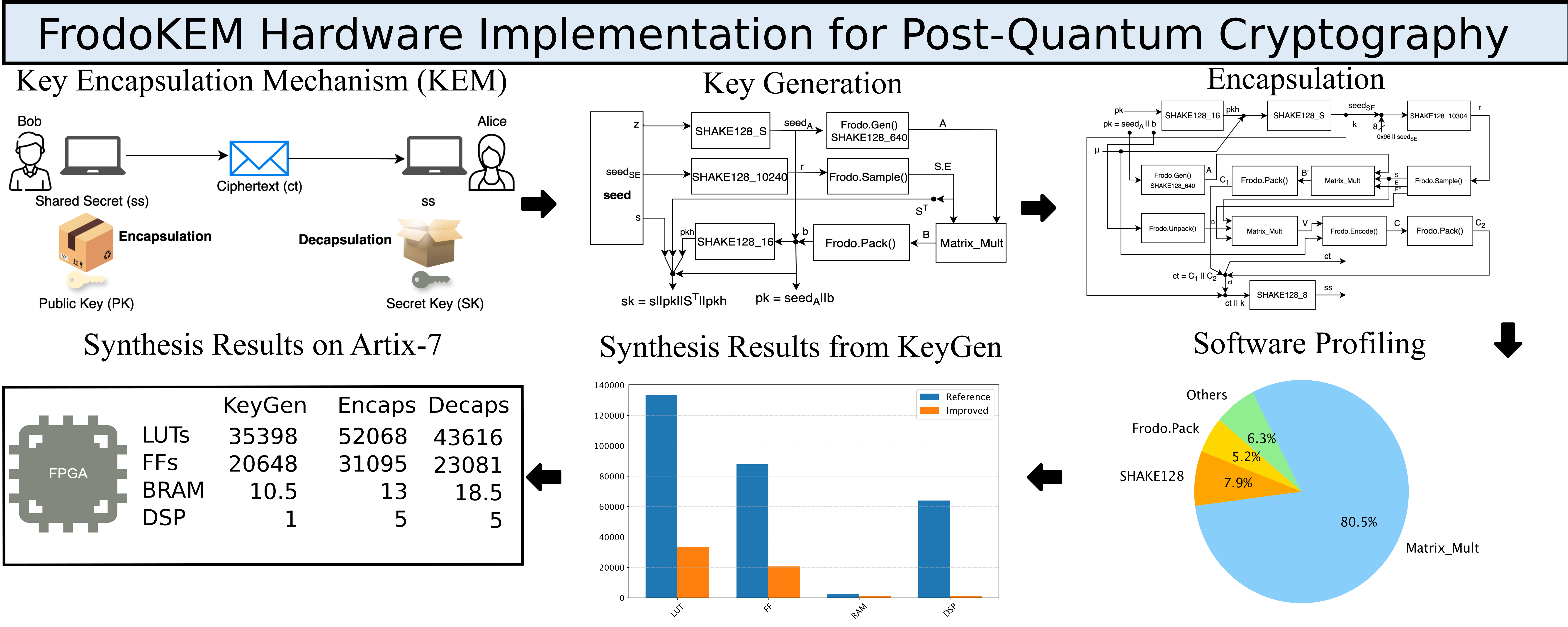

FrodoKEM Hardware Implementation for Post-Quantum Cryptography

Keywords:

Lattice-based cryptography, High-Level Synthesis (HLS), FPGA, Post-Quantum Cryptography, FrodoKEM, Hardware implementationAbstract

FrodoKEM, a key encapsulation mechanism (KEM) based on the learning with errors (LWE) problem, would be included for standardization by the International Organization for Standardization (ISO) and recommended for PQC migration by the BSI (German Federal Office for Information Security) and the ANSSI (French Cybersecurity Agency). It is closely related to the challenging time-computational problem inherent to algebraically unstructured lattices. However, hardware implementations of this scheme are required to verify its effectiveness in real-world applications. To the best of our knowledge, this is the first hardware implementation of FrodoKEM using High-Level Synthesis (HLS), which meets all requirements of the version submitted for standardization to ISO. The proposed design started with the profiling of the reference C software implementation using Valgrind software tools, to identify the functions that are the most time-consuming. The advantages of the proposed implementation include a 34% improvement in the speed metric of the Key Generation module in comparison with the reference software implementation. The results show that the key generation, encapsulation, and decapsulation use 26%, 39%, and 32%, respectively, of the total area utilization on the Artix-7.

Downloads

References

P. W. Shor, “Polynomial-time algorithms for prime factorization and discrete logarithms on a quantum computer,” SIAM Review, vol. 41, no. 2, pp. 303–332, 1999, doi: 10.1137/S0036144598347011, publisher: Society for Industrial and Applied Mathematics.

D. J. Bernstein, J. Buchmann, and E. Dahm´en, Eds., Post-quantum cryptography. Springer, 2009, doi: 10.1007/978-3-540-88702-7.

J. Howe, C. Moore, M. O’Neill, F. Regazzoni, T. G¨üneysu, and K. Beeden, “Lattice-based encryption over standard lattices in hardware,” in Proceedings of the 53rd Annual Design Automation Conference, ser. DAC’16. Association for Computing Machinery, 2016, doi: 10.1145/2897937.2898037, pp. 1–6.

J. Howe, T. Oder, M. Krausz, and T. G¨uneysu, “Standard lattice-based key encapsulation on embedded devices,” IACR Transactions on Cryptographic Hardware and Embedded Systems, pp. 372–393, 2018, doi: 10.13154/tches.v2018.i3.372-393.

N. I. of Standards and Technology, “SHA-3 standard: Permutation-based hash and extendable-output functions,” 2015.

J. Howe, M. Martinoli, E. Oswald, and F. Regazzoni, “Exploring parallelism to improve the performance of FrodoKEM in hardware,” Journal of Cryptographic Engineering, vol. 11, no. 4, pp. 317–327, 2021, doi: 10.1007/s13389-021-00258-7.

J. W. Bos, M. Ofner, J. Renes, T. Schneider, and C. Van Vredendaal, The Matrix Reloaded: Multiplication Strategies in FrodoKEM, M. Conti, M. Stevens, and S. Krenn, Eds. Springer International Publishing, 2021, doi: 10.1007/978-3-030-92548-2 5, vol. 13099, series Title: Lecture Notes in Computer Science.

E. Karabulut, E. Alkim, and A. Aysu, “Efficient, flexible, and constant-time Gaussian sampling hardware for lattice cryptography,” IEEE Transactions on Computers, pp. 1–1, 2021, doi: 10.1109/TC.2021.3107729.

V. B. Dang, F. Farahmand, M. Andrzejczak, and K. Gaj, “Implementing and benchmarking three lattice-based post-quantum cryptography algorithms using software/hardware codesign,” in 2019 International Conference on Field-Programmable Technology (ICFPT), 2019, doi: 10.1109/ICFPT47387.2019.00032, pp. 206–214.

V. L. R. D. Costa, J. López, and M. V. Ribeiro, “A System-on-a-Chip implementation of a post-quantum cryptography scheme for smart meter data communications,” vol. 22, no. 19, p. 7214, 2022, doi: 10.3390/s22197214.

K. Basu, D. Soni, M. Nabeel, and R. Karri, “NIST post-quantum cryptography- A hardware evaluation study,” 2019, publication info: Preprint. MINOR revision.

P. Karl, T. Fritzmann, and G. Sigl, “Hardware accelerated FrodoKEM on RISC-v,” in 2022 25th International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS). IEEE, 2022, doi: 10.1109/DDECS54261.2022.9770148, pp. 154–159.

N. Gupta, A. Jati, A. K. Chauhan, and A. Chattopadhyay, “PQC acceleration using GPUs: FrodoKEM, NewHope, and Kyber,” IEEE Transactions on Parallel and Distributed Systems, vol. 32, no. 3, pp.

–586, 2021, doi: 10.1109/TPDS.2020.3025691.

H. Kwon, K. Jang, H. Kim, H. Kim, M. Sim, S. Eum, W. K. Lee, and H. Seo, “ARMed frodo: FrodoKEM on 64-bit ARMv8 processors,” in Information Security Applications, H. Kim, Ed. Springer International Publishing, 2021, doi: 10.1007/978-3-030-89432-0 17, vol. 13009, pp. 206–217.

D. L. G. Filho, G. Brand˜ao, G. Adj, A. Alblooshi, I. A. Canales-Mart´ınez, J. Ch´avez-Saab, and J. L´opez, “PQC-AMX: Accelerating Saber and FrodoKEM on the Apple M1 and M3 SoCs,” in 2024 IEEE 31st Symposium on Computer Arithmetic (ARITH). IEEE, 2024, doi: 10.1109/ARITH61463.2024.00012, pp. 9–16.

O. Regev, “On lattices, learning with errors, random linear codes, and cryptography,” in Proceedings of the 37th annual ACM Symposium on Theory and Computing - STOC’05, 2005, doi: 10.1145/1568318.15683, pp. 84 – 93.

F. Team, “FrodoKEM specification,” 2023. [Online]. Available: www.frodokem.org

F. A. Urbano-Molano, and J. Velasco-Medina, “SHA-3 implementation for post-quantum cryptography using high-level synthesis,” in XI Southern Programmable Logic Conference, 2023, pp. 9–12.

C.-H. Lee, J.-H. Lee, H. Jung, H. Lee, and H. Lee, “HLS-based HW/SW co-design and hybrid HLS-RTL design for post-quantum cryptosystem,” Journal of Semiconductor Technology and Science, vol. 24, no. 3, pp. 191–198, 2024, doi: 10.5573/JSTS.2024.24.3.191.

C. Aguilar-Melchor, J.-C. Deneuville, A. Dion, J. Howe, R. Malmain, V. Migliore, M. Nawan, and K. Nawaz, “Towards automating cryptographic hardware implementations: A case study of HQC,” in Code-Based Cryptography, J.-C. Deneuville, Ed. Springer Nature Switzerland, 2023, doi: 10.1007/978-3-031-29689-5 4, vol. 13839, pp. 62–76, series Title: Lecture Notes in Computer Science.

G. Montanaro, A. Galimberti, E. Colizzi, and D. Zoni, “Hardware-software co-design of BIKE with HLS-generated accelerators,” in 2022 29th IEEE International Conference on Electronics, Circuits, and Systems (ICECS). IEEE, 2022, doi: 10.1109/ICECS202256217.2022.9970992, pp. 1–4.