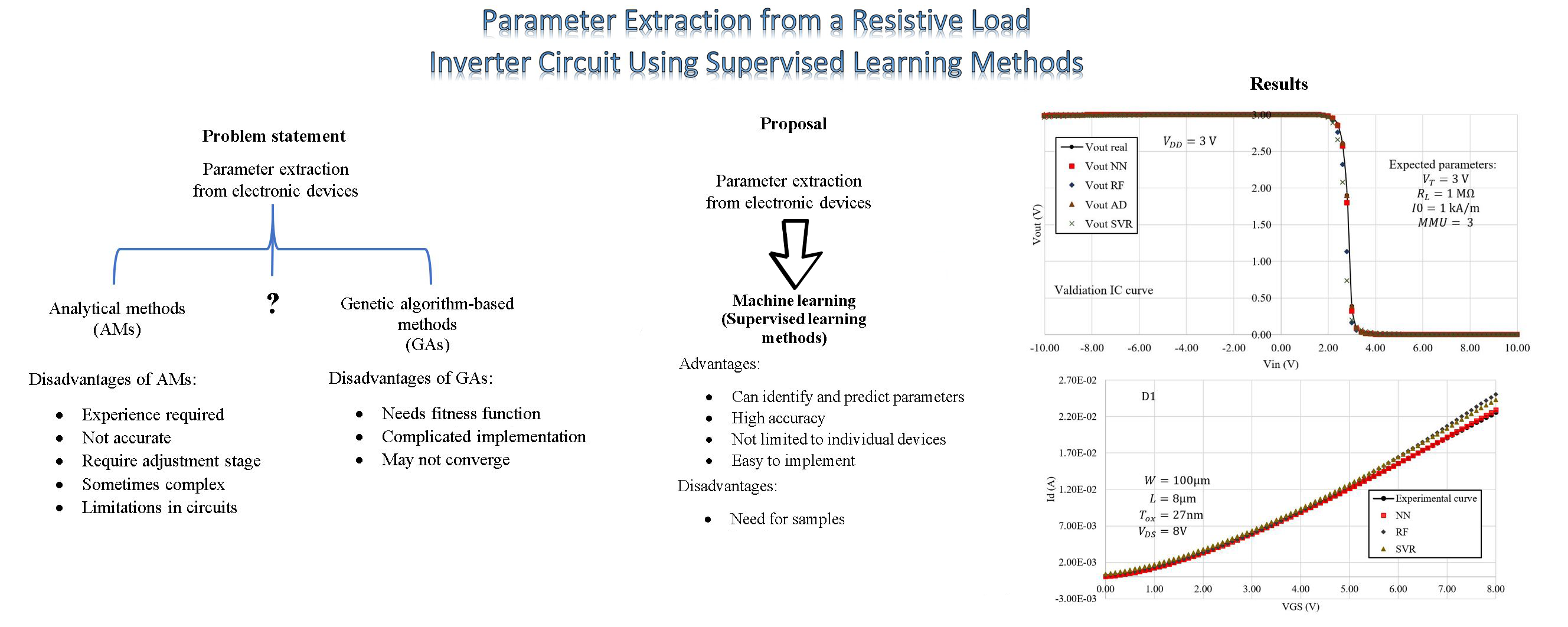

Parameter Extraction from a Resistive Load Inverter Circuit Using Supervised Learning Methods

Keywords:

Inverter circuit, Parameter extraction, Supervised learning, Modeling, Electronic simulationAbstract

This paper presents a proposal for parameter extraction of a resistive load inverter circuit, with a Thin Film Transistor (TFT), using Artificial Neural Networks, Random Forest, Decision Trees and Support Vector Regression. Although analytical and optimization methods are usually used for this purpose, they have disadvantages such as the need for expertise or complex implementation. This work shows that these supervised learning methods are useful for this task because they can learn the parameters of the device transfer curves, obtaining a good fit between the measurements and the extracted parameters. The different methods were trained using a data set constructed from simulations performed with AIM-Spice software, where the parameters affecting different regions of the inverter characteristic curve were extracted. In the experimental stage, the Neural Networks obtained better results, with an average error rate of 6.04%. The method was also applied to real NMOS measurements and yielded minimum errors of up to 0.43%.

Downloads

References

A. Ortiz-Conde, F. J. García-Sánchez, J. Muci, A. Terán Barrios, J. J. Liou, and C.-S. Ho, “Revisiting MOSFET threshold voltage extraction methods,” Microelectron. Reliab., vol. 53, no. 1, pp. 90–104, Jan. 2013, doi: 10.1016/j.microrel.2012.09.015.

A. Cerdeira, M. Estrada, R. Garcı́a, A. Ortiz-Conde, and F. J. Garcı́a Sánchez, “New procedure for the extraction of basic a-Si:H TFT model parameters in the linear and saturation regions,” Solid. State. Electron., vol. 45, no. 7, pp. 1077–1080, Jul. 2001, doi: 10.1016/S0038-1101(01)00143-5.

C. Tanaka and K. Ikeda, “Comprehensive investigation on parameter extraction methodology for short channel amorphous-InGaZnO thin-film transistors,” in 2018 IEEE International Conference on Microelectronic Test Structures (ICMTS), Mar. 2018, pp. 23–26, doi: 10.1109/ICMTS.2018.8383756.

Y. H. Hu and S. Pan, “SaPOSM: an optimization method applied to parameter extraction of MOSFET models,” IEEE Trans. Comput. Des. Integr. Circuits Syst., vol. 12, no. 10, pp. 1481–1487, 1993, doi: 10.1109/43.256940.

P. Moreno, R. Picos, M. Roca, E. Garcia-Moreno, B. Iniguez, and M. Estrada, “Parameter Extraction Method using Genetic Algorithms for an Improved OTFT Compact Model,” in 2007 Spanish Conference on Electron Devices, Jan. 2007, pp. 64–67, doi: 10.1109/SCED.2007.383996.

N. Akkan, M. Altun, and H. Sedef, “Parameter Extraction Method Using Hybrid Artificial Bee Colony Algorithm for an OFET Compact Model,” in 2018 15th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Jul. 2018, pp. 105–108, doi: 10.1109/SMACD.2018.8434861.

I. Benacer and Z. Dibi, “Extracting parameters of OFET before and after threshold voltage using genetic algorithms,” Int. J. Autom. Comput., vol. 13, no. 4, pp. 382–391, Aug. 2016, doi: 10.1007/s11633-015-0918-6.

N. Akkan, M. Altun, and H. Sedef, “Modeling and Parameter Extraction of OFET Compact Models Using Metaheuristics-Based Approach,” IEEE Access, vol. 7, pp. 180438–180450, 2019, doi: 10.1109/ACCESS.2019.2959474.

T. Bendib and F. Djeffal, “Electrical Performance Optimization of Nanoscale Double-Gate MOSFETs Using Multiobjective Genetic Algorithms,” IEEE Trans. Electron Devices, vol. 58, no. 11, pp. 3743–3750, Nov. 2011, doi: 10.1109/TED.2011.2163820.

E. Gadjeva and M. Hristov, “Computer-aided extraction of small-signal model parameters of heterojunction bipolar transistors,” in Proceedings of the Joint INDS’11 & ISTET’11, Jul. 2011, pp. 1–6, doi: 10.1109/INDS.2011.6024817.

A. Huang, Z. Zhong, Y. Guo, and W. Wu, “A novel extrinsic parameter extraction method for the technology independent modeling of transistors,” in 2015 Asia-Pacific Microwave Conference (APMC), Dec. 2015, pp. 1–2, doi: 10.1109/APMC.2015.7412946.

A. Jarndal, “Combined genetic algorithm and neural network technique for transistor modeling,” in 2015 International Conference on Communications, Signal Processing, and their Applications (ICCSPA’15), Feb. 2015, pp. 1–4, doi: 10.1109/ICCSPA.2015.7081300.

S. I. Sayed, M. M. Abutaleb, and Z. B. Nossair, “Improved CNFET performance based on genetic algorithm parameters optimization,” in 2017 8th IEEE Annual Information Technology, Electronics and Mobile Communication Conference (IEMCON), Oct. 2017, pp. 181–184, doi: 10.1109/IEMCON.2017.8117185.

S. Moparthi, P. K. Tiwari, and G. K. Saramekala, “Genetic algorithm-based threshold voltage prediction of SOI JLT using multi-variable nonlinear regression,” in 2021 International Symposium on Devices, Circuits and Systems (ISDCS), Mar. 2021, pp. 1–4, doi: 10.1109/ISDCS52006.2021.9397911.

R. Picos, O. Calvo, B. Iñiguez, E. García-Moreno, R. García, and M. Estrada, “Optimized parameter extraction using fuzzy logic,” Solid. State. Electron., vol. 51, no. 5, pp. 683–690, May 2007, doi: 10.1016/j.sse.2007.02.031.

K. R. Chowdhary, Fundamentals of artificial intelligence. New Delhi: Springer India, 2020.

J. J. Grefenstette, Ed., Genetic Algorithms for Machine Learning. Boston, MA: Springer US, 1994.

S. Bandyopadhyay and S. Kumar, Classification and Learning Using Genetic Algorithms. Berlin, Heidelberg: Springer Berlin Heidelberg, 2007.

L. Zhang, Y. Pan, X. Wu, and M. J. Skibniewski, Introduction to Artificial Intelligence, vol. 163. London: Springer London, 2021.

R. H. Griffin, D. E. Root, J. Xu, A. Dadvand, T. Y. Chu, and Y. Tao, “Artificial Neural Network Modelling and Simulation of Organic Field Effect Transistors and Circuits,” in 2019 IEEE International Flexible Electronics Technology Conference, IFETC 2019, Aug. 2019, pp. 1–5, doi: 10.1109/IFETC46817.2019.9073711.

J. Cai, J. King, C. Yu, J. Liu, and L. Sun, “Support Vector Regression-Based Behavioral Modeling Technique for RF Power Transistors,” IEEE Microw. Wirel. Components Lett., vol. 28, no. 5, pp. 428–430, May 2018, doi: 10.1109/LMWC.2018.2819427.

J. Cai, C. Yu, J. Liu, and L. Sun, “Large Signal Behavioral Model of RF Transistor Using Least Square Support Vector Machine,” in 2020 International Conference on Microwave and Millimeter Wave Technology (ICMMT), Sep. 2020, pp. 1–3, doi: 10.1109/ICMMT49418.2020.9386908.

L. Puggini, J. Doyle, and S. McLoone, “Fault Detection using Random Forest Similarity Distance,” IFAC-PapersOnLine, vol. 48, no. 21, pp. 583–588, 2015, doi: 10.1016/j.ifacol.2015.09.589.

A. Ojha, Y. S. Chauhan, and N. R. Mohapatra, “A Channel Stress-Profile-Based Compact Model for Threshold Voltage Prediction of Uniaxial Strained HKMG nMOS Transistors,” IEEE J. Electron Devices Soc., vol. 4, no. 2, pp. 42–49, Mar. 2016, doi: 10.1109/JEDS.2016.2524536.

C.-H. Shen, Y. Li, I.-H. Lo, P.-J. Lin, and S.-C. Chung, “Modeling temperature and bias stress effects on threshold voltage of a-Si:H TFTs for gate driver circuit simulation,” in 2011 International Conference on Simulation of Semiconductor Processes and Devices, Sep. 2011, pp. 251–254, doi: 10.1109/SISPAD.2011.6035072.

Berkeley, “Aim-Spice.” California, [Online]. Available: http://www.aimspice.com/.

B. M. Wilamowski and J. D. Irwin, The Industrial Electronics Handbook: Intelligent Systems, Second. CRC Press, 2011.

A. B. Kock and T. Teräsvirta, “Forecasting performances of three automated modelling techniques during the economic crisis 2007–2009,” Int. J. Forecast., vol. 30, no. 3, pp. 616–631, Jul. 2014, doi: 10.1016/j.ijforecast.2013.01.003.

M. Hagan, H. Demuth, M. Beale, and O. De Jesus, Neural Network Design, Second. Ebook, 2014.

S. Raschka and V. Mirjalili, Python Machine Learning, Second Edi. Birmingham: Packt Publishing Ltd., 2017.

A. C. Muller and S. Guido, Introduction to Machine Learning with Python. United States of America: O’Reilly Media, 2016.

G. James, D. Witten, T. Hastie, and R. Tibshirani, An Introduction to Statistical Learning, vol. 103. New York, NY: Springer New York, 2013.