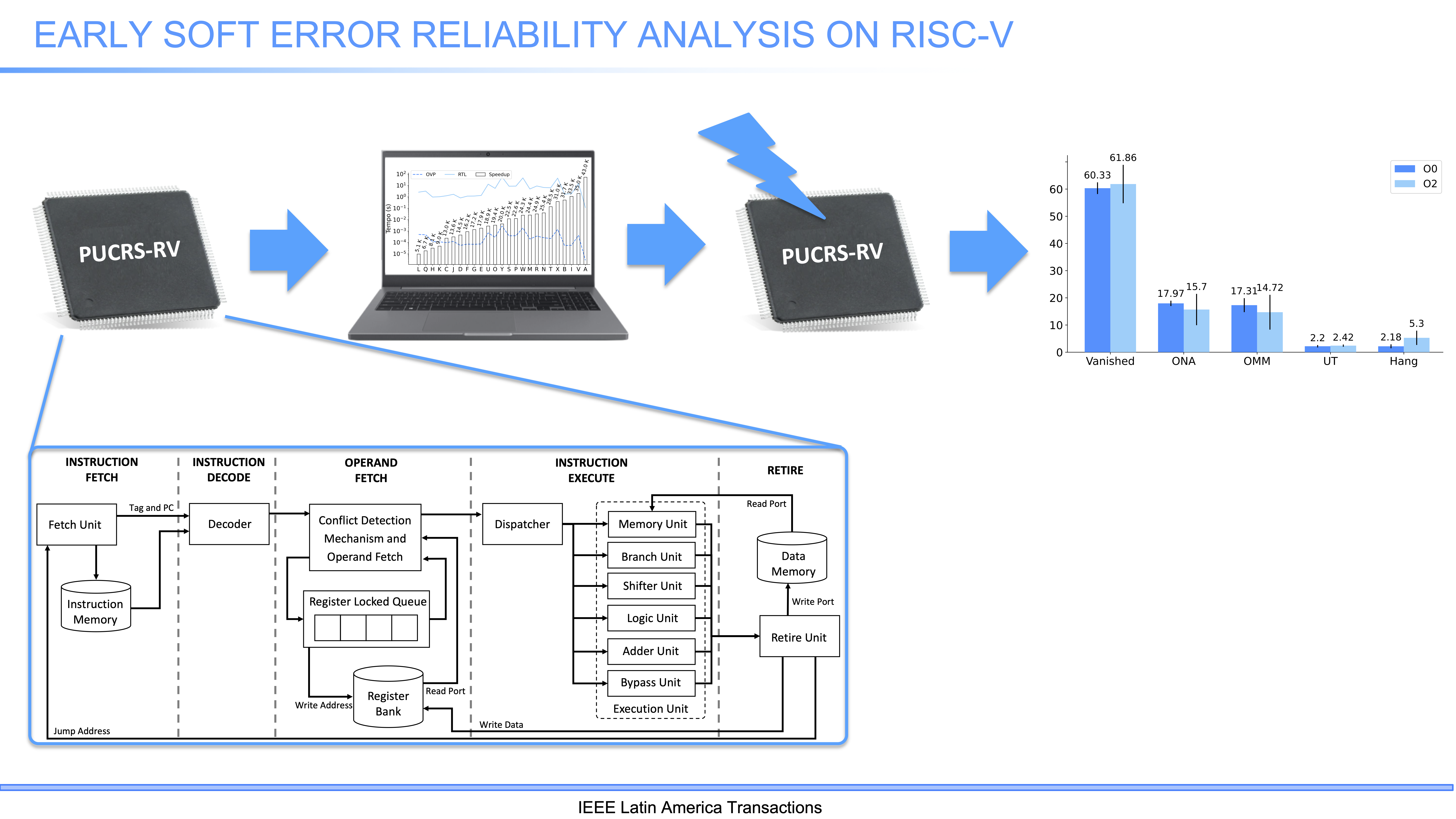

Early Soft Error Reliability Analysis on RISC-V

Keywords:

Reliability, RISC-V, Soft Error, Fault InjectionAbstract

The adoption of RISC-V processors bloomed in recent years, mainly due to its open standard and free instruction set architecture. However, much remains to help software engineers deliver high-reliability and bug-free applications and systems based on RISC-V IP designs. This work proposes an early soft error reliability assessment of a RISC-V processor, extending the previously proposed SOFIA fault injection framework. Results from 850k fault injections show that choosing the compiler flag -O2 to optimize performance causes 96% more Hang failures than -O0. Software engineers must evaluate compilation parameters on a case-by-case basis to find the best balance between performance and reliability. This work helps software engineers develop fault-tolerant RISC-V-based systems and applications more efficiently.

Downloads

References

Z. Zou, Y. Jin, P. Nevalainen, Y. Huan, J. Heikkonen, and T. Westerlund, “Edge and Fog Computing Enabled AI for IoT - An Overview,” in AICAS, 2019, pp. 51–56.

P.-K. Huang and S. Ghiasi, “Power-Aware Compilation for Embedded Processors with Dynamic Voltage Scaling and Adaptive Body Biasing Capabilities,” in DATE, 2006, pp. 1–2.

A. Waterman, Y. Lee, D. A. Patterson, and K. Asanovic, “The RISC- V Instruction Set Manual, Volume I: UserLevel ISA, Version 2.1,” UCB/EECS-2016-118, UC Berkeley, Tech. Rep., 2016.

S. Greengard, “Will RISC-V Revolutionize Computing?” Communications of the ACM, vol. 63, no. 5, pp. 30–32, 2020.

M. Snir, R. W. Wisniewski, J. A. Abraham, S. V. Adve, S. Bagchi, P. Balaji, J. Belak, P. Bose, F. Cappello, B. Carlson, A. A. Chien, P. Coteus, N. A. Debardeleben, P. C. Diniz, C. Engelmann, M. Erez, S. Fazzari, A. Geist, R. Gupta, F. Johnson, S. Krishnamoorthy, S. Leyffer, D. Liberty, S. Mitra, T. Munson, R. Schreiber, J. Stearley, and E. V. Hensbergen, “Addressing Failures in Exascale Computing,” International Journal of High Performance Computing Applications, vol. 28, no. 2, pp. 129–173, 2014.

F. R. da Rosa, R. Garibotti, L. Ost, and R. Reis, “Using Machine Learning Techniques to Evaluate Multicore Soft Error Reliability,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 66, no. 6, pp. 2151–2164, 2019.

M. G. Trindade, R. P. Bastos, R. Garibotti, L. Ost, M. Letiche, and J. Beaucour, “Assessment of Machine Learning Algorithms for Near-Sensor Computing under Radiation Soft Errors,” in ICECS, 2020, pp. 1–4.

V. Bandeira, J. Sampford, R. Garibotti, M. G. Trindade, R. P. Bastos, R. Reis, and L. Ost, “Impact of radiation-induced soft error on embedded cryptography algorithms,” Microelectronics Reliability, p. 114349, 2021.

G. Abich, J. Gava, R. Garibotti, R. Reis, and L. Ost, “Applying Lightweight Soft Error Mitigation Techniques to Embedded Mixed Precision Deep Neural Networks,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 68, no. 11, pp. 4772–4782, 2021.

G. Abich, R. Garibotti, R. Reis, and L. Ost, “The Impact of Soft Errors in Memory Units of Edge Devices Executing Convolutional Neural Networks,” IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 69, no. 3, pp. 679–683, 2022.

H. Cho, S. Mirkhani, C.-Y. Cher, J. A. Abraham, and S. Mitra, “Quantitative Evaluation of Soft Error Injection Techniques for Robust System Design,” in DAC, 2013, pp. 1–10.

A. Akram, V. Akella, S. Peisert, and J. Lowe-Power, “Enabling Design Space Exploration for RISC-V Secure Compute Environments,” Berkeley Lab., 2022. [Online]. Available: https://escholarship.org/uc/item/0nt7h5jm

K. Parasyris, G. Tziantzoulis, C. D. Antonopoulos, and N. Bellas, “GemFI: A Fault Injection Tool for Studying the Behavior of Applications on Unreliable Substrates,” in DSN, 2014, pp. 622–629.

G. Abich, R. Garibotti, V. Bandeira, F. Rosa, J. Gava, F. Bortolon, G. Medeiros, F. G. Moraes, R. Reis, and L. Ost, “Evaluation of the soft error assessment consistency of a JIT-based virtual platform simulator,” IET Computers & Digital Techniques, vol. 15, no. 2, pp. 125–142, 2021.

A. E. Wilson and M. Wirthlin, “Neutron Radiation Testing of Fault Tolerant RISC-V Soft Processor on Xilinx SRAM-based FPGAs,” in SCC, 2019, pp. 25–32.

A. B. de Oliveira, L. A. Tambara, F. Benevenuti, L. A. C. Benites, N. Added, V. A. P. Aguiar, N. H. Medina, M. A. G. Silveira, and F. L. Kastensmidt, “Evaluating Soft Core RISC-V Processor in SRAM-Based FPGA Under Radiation Effects,” IEEE Transactions on Nuclear Science, vol. 67, no. 7, pp. 1503–1510, 2020.

A. Ramos, J. A. Maestro, and P. Reviriego, “Characterizing a RISC-V SRAM-based FPGA implementation against Single Event Upsets using fault injection,” Microelectronics Reliability, vol. 78, pp. 205–211, 2017.

H. Cho, “Impact of Microarchitectural Differences of RISC-V Processor Cores on Soft Error Effects,” IEEE Access, vol. 6, pp. 41302–41313, 2018.

A. Ramos, R. G. Toral, P. Reviriego, and J. A. Maestro, “An ALU Protection Methodology for Soft Processors on SRAM-Based FPGAs,” IEEE Transactions on Computers, vol. 68, no. 9, pp. 1404–1410, 2019.

I. Wali, A. Sánchez-Macián, A. Ramos, and J. A. Maestro, “Analyzing the impact of the Operating System on the Reliability of a RISC-V FPGA Implementation,” in ICECS, 2020, pp. 1–4.

I. Marques, C. Rodrigues, A. Tavares, S. Pinto, and T. Gomes, “Lock-V: A heterogeneous fault tolerance architecture based on Arm and RISC- V,” Microelectronics Reliability, vol. 120, p. 114120, 2021.

Z. Mohseni and P. Reviriego, “Reliability characterization and activity analysis of lowRISC internal modules against single event upsets using fault injection and RTL simulation,” Microprocessors and Microsystems, vol. 71, p. 102871, 2019.

S. Gupta, N. Gala, G. S. Madhusudan, and V. Kamakoti, “SHAKTI-F: A Fault Tolerant Microprocessor Architecture,” in ATS, 2015, pp. 163–168.

D. A. Santos, L. M. Luza, C. A. Zeferino, L. Dilillo, and D. R. Melo, “A Low-Cost Fault-Tolerant RISC-V Processor for Space Systems,” in DTIS, 2020, pp. 1–5.

V. Bandeira, F. Rosa, R. Reis, and L. Ost, “Non-intrusive Fault Injection Techniques for Efficient Soft Error Vulnerability Analysis,” in VLSI-SoC, 2019, pp. 123–128.

S. Feng, S. Gupta, A. Ansari, and S. Mahlke, “Shoestring: Probabilistic Soft Error Reliability on the Cheap,” in ASPLOS, 2010, pp. 385–396.

Imperas, “DEV - Virtual Platform Development and Simulation,” 2022. [Online]. Available: https://www.imperas.com/dev-virtual-platform-development-and-simulation

M. L. L. Sartori and N. L. V. Calazans, “Go Functional Model for a RISC-V Asynchronous Organisation - ARV,” in ICECS, 2017, pp. 381–348.

M. Krzywinski and N. Altman, “Points of significance: Significance, P values and t-tests,” Nature Methods, vol. 10, no. 11, pp. 1041–1042, 2013.

R. Leveugle, A. Calvez, P. Maistri, and P. Vanhauwaert, “Statistical Fault Injection: Quantified Error and Confidence,” in DATE, 2009, pp. 502–506.

J. Gustafsson, A. Betts, A. Ermedahl, and B. Lisper, “The mälardalen WCET benchmarks: past, present and future,” in WCET, 2010, pp. 136–146.