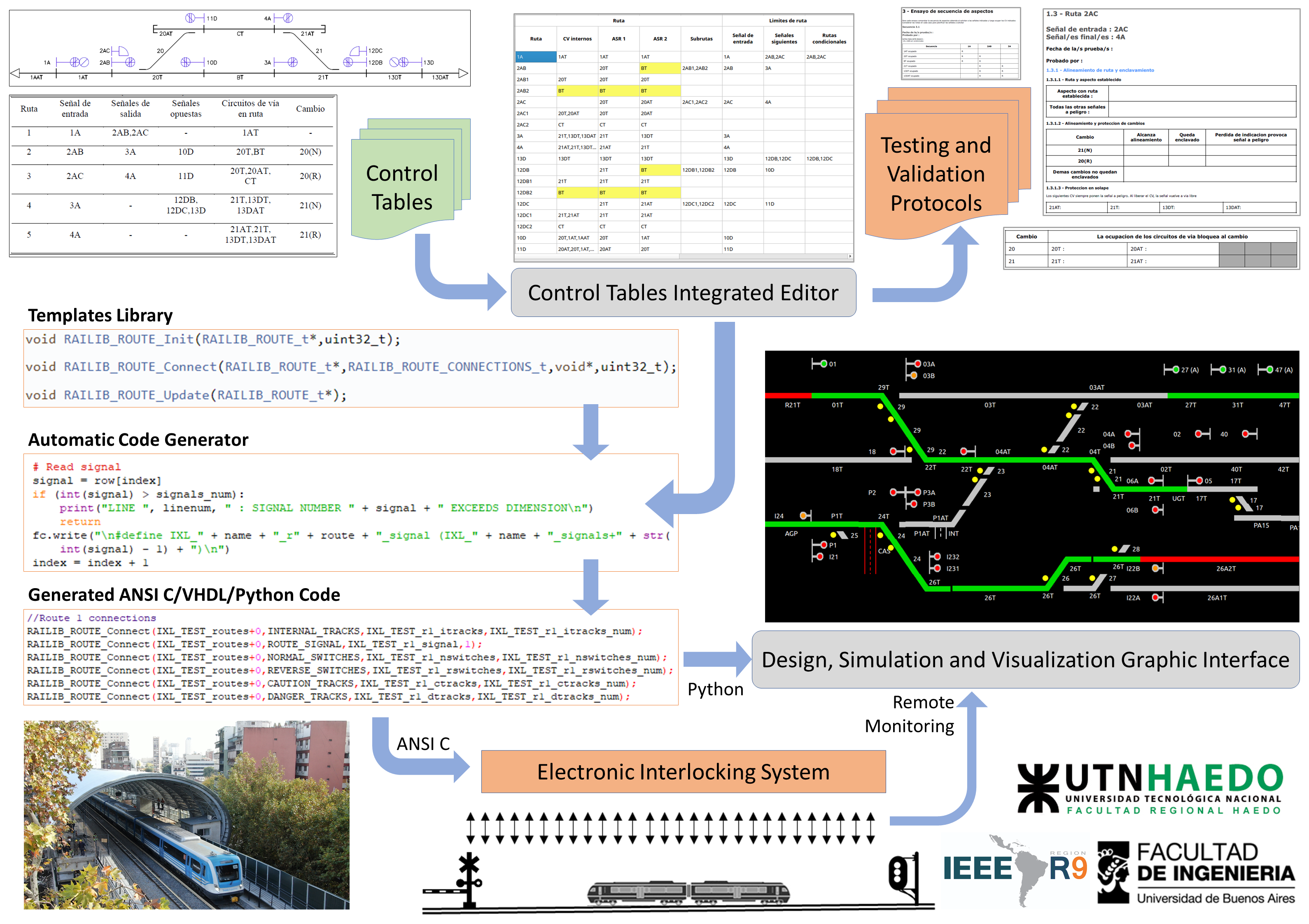

Modelling, Simulation and Code Generation for Electronic Railway Interlocking Systems

Keywords:

Railway interlocking, automatic code generation, object-oriented programming, functional safety, critical systems, FPGAAbstract

Electronic railway interlockings are critical embedded systems which control the safe operation of train signals. Due to the broad variety of railway network topologies and the high functional safety level required for these critical systems, a flexible solution is needed, capable of taking formal requirements and implementing them accordingly to the required application. The scope of this work is to present an approach in which from the standard specification of the system, a model is created and from this model the embedded system firmware is generated. The proposed framework comprises an automatic code generator that transforms the control tables which describe the interlocking logic into functional units written in different programming languages like C, Python or VHDL. Then, the generated code is linked with a class library that allows its implementation in an embedded system based in a FPGA or a microcontroller. In addition, the project contains a graphical user interface to draw the signaling layout and simulate the operation and behavior of the generated model for verification purposes.

Downloads