# A Novel Transformerless Ultra Gain DC-DC Converter for Renewable Micro Energy Sources

Kuraganti Manikanta (b), and Ramulu Chinthamalla (b), Senior Member, IEEE

Abstract—This article proposes a novel Ultra Gain Cubic (UGC) DC-DC converter for integrating PV and Fuel cell into the grid. The proposed UGC converter is unique for its minimum component count, particularly for obtaining ultra gain when compared to existing DC-DC converters. The steady-state operation of the converter in both modes were explained and necessary equations were derived. The effect of parasitic elements on the UGC's DC-voltage gain is examined, and the stability of the UGC converter is verified using the state space averaging technique. Minimum number of components, ultra voltage gain, input and output terminals are connected to same ground, single switch, input current continuous are the key aspects of the UGC converter. A 300 W prototype with a 325 V output voltage is tested and validated using hardware results.

Link to graphical and video abstracts, and to code: https://latamt.ieeer9.org/index.php/transactions/article/view/8749

Index Terms—Ultra gain, Single switch, DC-DC converter, CCM, DCM, BCM .

### I. INTRODUCTION

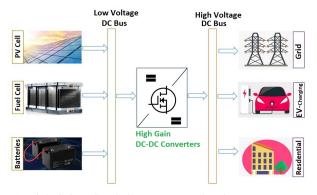

$\mathbf{R}$  ecent increase in the price of fossil fuels, and new laws restricting  $CO_2$  emissions have raised interest in renewable energy options globally [1]. Solar and fuel cell technologies are well-known sources of renewable energy and have drawn a lot of attention. The output voltages of fuel cells and solar photovoltaics are extremely low [2]. Therefore, these low-voltage DC voltages are converted to high DC voltages (310 V - 600 V) by employing high-gain DC-DC converters, which also serve as a bridge between the source and the load. The applications of high voltage DC bus are shown in Fig. 1. Although conventional converters have the ability to boost the

Fig. 1. High Gain DC-DC Converter: Need and Uses.

K. Manikanta, and R. Chinthamalla are with the National Institute of Technology, Warangal, India (e-mails: km21eerer13@student.nitw.ac.in, and rnitchinthamalla@nitw.ac.in).

voltage, parasitic elements limit their gain [3]-[4].

Numerous converters have been reported by researchers with notable voltage gains, in an effort to fulfill the condition stated earlier [5]-[29]. By altering the transformer's turns ratio, isolated converters provide significant gains. Additionally, inputoutput isolation and safety are provided by isolated converters [6]. However, the stored leakage energy of inductors causes significant voltage spikes across the switches, necessitating extra circuitry to reduce these spikes, leading to an increased total cost [7]. Therefore, non-isolated DC-DC converters are better suited for attaining high voltage. The following set of major contributions highlights the importance of non-isolated converters. In [8], a modified SEPIC converter with a gain of  $\frac{1+d}{(1-d)}$  is described, which requires two switches. In contrast, [9] achieves the same gain as [8], but with the extra benefit of just requiring one switch. A transformer-less step-up converter with a gain of  $\frac{2}{(1-d)}$  is described in [10], which is superior to both [8] and [9]. On the other hand, it too requires two switches for operation, just like [8]. Remarkably, all three designs [8], [9], and [10] use only eight components, despite their differences.

[11] presents an enhanced SEPIC converter with a gain of  $\frac{1+3d}{(1-d)}$ , yet it suffer from common ground issues. In contrast [12] introduces a switched capacitor topology using regenerative network, offering a gain of  $\frac{2-d}{(1-d)^2}$ .

Both [11] and [12] use ten components, but [12] achieves a higher gain than [11] and incorporates a common ground feature. Nonetheless, its gain increase is moderate, and it still necessitates the use of two switches.

The topologies discussed from [8] to [12] are lower component count and cost-effective. Common ground problems, limited gain increase, and the need for multiple switches are some of the problems they face.

A switched capacitor (SC) boost converter is reported in [13]. Unfortunately, its efficiency is reduced by significant transient capacitor currents and it requires more number of capacitors.

Using coupled inductors is another method of enhancing voltage gain. However, leakage energy causes semiconductor devices to experience huge spikes in voltage and current and necessitates accurate inductors [14]. ZVS and ZCS techniques [15] can be used to reduce voltage spikes in coupled circuits. However, it requires additional components, making the overall system bulky and expensive.

The three level boost converter with less voltage stress across switches is reported in [16]. However, its gain is same as conventional boost.

According to the one mentioned in [17] has high gain at

lower duty ratios but having discontinuous input current and high input current ripple. An interleaved technique [18] can be used to reduce input current ripple, but it involves a more complex control circuit and additional components.

There have been several high voltage gain converters introduced in [19]–[20] that are based on voltage Multipliers (VM). It's possible for voltage multipliers to reduce the voltage stress across switching devices and make these converters much more voltage gain-oriented. To achieve high gains, though, more components of diodes and capacitors are needed.

The paper [21] suggests a cascaded boost converter that contains a single switch and achieves a gain that is equal to the square of a buck-boost converter. In contrast, the efficiency is lower and the gain enhancement is less. A VM -based converter has been reported in [22] that further increases voltage gain with a gain of  $\frac{2+2d}{(1-d)}$ . Even with seven capacitors and three inductors, the gain is not that much improved.

According to the aforementioned literature, existing converters have several common problems, including low voltage gain, more number of components, bulky, common ground issues and low efficiency. Therefore, this article aims to overcome the mentioned limitations by introducing a novel switched LC network-based UGC converter.

# II. CIRCUIT TOPOLOGY AND OPERATION

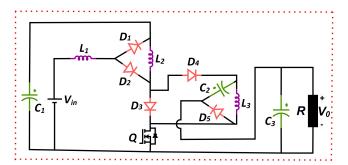

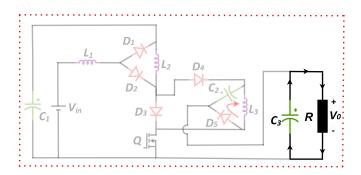

For the integration of renewable energy sources into the grid, conventional boost, cuk, and flyback converters are commonly utilized. However, their gain is limited by parasitic elements, and efficiency degrades when voltage levels are higher. Therefore, the proposed UGC converter shown in Fig. 2 is a promising solution to overcome these limitations and facilitate the efficient integration of renewable energy.

Fig. 2. The UGC converter.

The UGC converter has the following benefits over existing topologies

- 1. Ultra gain is achieved with minimum number of components

- 2. To get cubic gains, only one switch is needed.

- 3. The proposed converter provides a theoretical gain of 125 at d @ 0.8.

- 4. Without using any transformer or coupled inductors, the proposed UGC converter attaining higher gains. So high power density and overall cost is low.

- 5. Input current continuous, high efficiency (>90%), input and output are connected to same ground, are some additional advantages of the UGC converter.

The operating modes and waveforms in CCM and DCM were described, and the necessary equations were derived.

### A. Continuous Conduction Mode

Mode-I [ $t_0$  -  $t_1$ ]:- As shown in Fig. 3, inductors  $L_1$  , $L_2$  and  $L_3$  begin charging linearly when switch Q is in the ON state.  $V_{in}$  charges inductor  $L_1$ , capacitor  $C_1$  charges inductor  $L_2$ , and energy stored in filter capacitor  $C_3$  charges both inductor  $L_3$  and capacitor  $C_2$ .

The theoretical waveforms of mode-I are presented in Fig. 5. The subsequent equations were derived using KVL and KCL.

Fig. 3. Mode-I circuit diagram.

$$V_{L_1} - V_{in} = 0, V_{L_2} - V_{C_1} = 0 \& V_{L_3} - V_0 + V_{C_2} = 0$$

(1)

$$i_{C1(ON)} = -i_{L2}, i_{C2(ON)} = i_{L3}, i_{C3(ON)} = -i_{L3} - i_0$$

(2)

The above equations show that the circuit is operating as an ideal model, with the parasitic voltage drops of passive components and the ON-state resistance drops of switches and diodes being neglected. However, the model with these losses will be clearly discussed in the upcoming section.

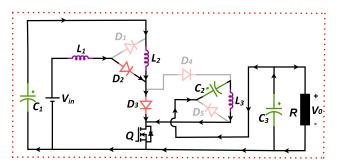

Mode-II  $[t_1 - t_2]$ :- Upon turning off switch Q, the stored energy of inductor  $L_1$  is released into capacitor  $C_1$ , whereas inductor  $L_3$  releases its stored energy into capacitor  $C_2$ . Additionally, to filter capacitor  $C_3$  and load, inductors  $L_1$ ,  $L_2$ , and  $C_2$  are discharged in conjunction with source voltage which is shown in Fig. 4.

Fig. 4. Mode-II operation.

$$V_{L1} - V_{in} + V_{C1} = 0, \ V_{L2} - V_{C1} - V_{C2} + V_0 = 0, V_{L3} + V_{C2} = 0$$

and

$$i_{C1(OFF)} = i_{L1} - i_{L2}, i_{C2(OFF)} = i_{L3} - i_{L2}, i_{C3(OFF)} = i_0 - i_{L2}$$

(4)

The voltage gain of the UGC converter in CCM  $(G_{VCCM})$  is derived by applying the Volt-Sec balance equation for inductors, and it is obtained as

$$G_{VCCM} = \frac{1}{(1-d)^3}$$

(5)

By using Charge-Sec balance equation for capacitors  $C_1, C_2$  and  $C_3$ , the current gain of UGC converter in CCM  $(G_{ICCM})$  is obtained as

$$G_{ICCM} = (1 - d)^3 \tag{6}$$

Fig. 5. Analytical waveforms in CCM and DCM modes.

# B. Discontinuous Conduction Mode

The operating modes and corresponding theoretical waveforms in DCM are presented in Fig. 5.

Mode-I  $[t_0 - t_1]$ :- In terms of operation, this mode works similarly to Mode-I CCM. The peak value of inductor current  $L_3$  is given by

$$i_{L_3} = \left(\frac{V_{in}}{\left(1 - d\right)^2}\right) \times \frac{dT}{L_3} \tag{7}$$

Mode-II  $[t_1 - t_2]$ :- In this stage, the inductor current  $L_3$  begins to decrease and eventually drops to zero at  $t = t_x$ . Apart from this, the remaining working operation and current paths same as Mode-II in CCM.

$$i_{L_3} = (V_0 d) \times \frac{d_z T}{L_3} \tag{8}$$

where  $d_z$  is unknown duty ratio which can be calculated by equating (7) and (8).

$$d_z = \left(\frac{V_{in} \times d}{V_0 (1 - d)^2}\right) \tag{9}$$

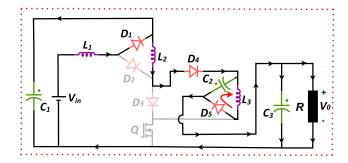

Mode III  $[t_2 - t_3]$ : As switch Q is turned OFF, inductor current  $L_3$  becomes zero at moment  $t = t_3$ . The average output filter

Fig. 6. Mode-III circuit diagram.

capacitor current shown in Fig. 6 is expressed as,

$$I_{C0} = \frac{1}{2} d_z I_{Lp3} - i_0 = 0 {10}$$

Substitute (7),(9) in (10). After simplification, the voltage gain in DCM  $(k_{DCM})$  is derived as

$$k_{DCM} = \frac{1}{(1+2d-d^2)} \left[ \sqrt{\frac{d}{2\tau}} \right]$$

(11)

where,

$$\tau = \frac{L_3.f_s}{R}$$

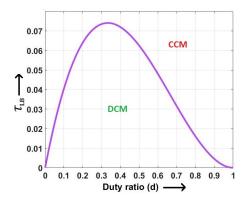

#### C. Boundary conditions Mode

Under BCM mode, At particular instant of time inductor current shifts from continuous conduction mode to discontinuous conduction mode.

Both CCM and DCM's voltage gains are equal at this moment.

Fig. 7. CCM And DCM boundary plot.

So, by equating (5), (11) the boundary duty constant  $(\tau_{LB})$  of inductor  $L_3$  is obtained as

$$\tau_{LB} = \frac{d.(1-d)^2}{2} \tag{12}$$

The relation between boundary duty constant and duty ratio is plotted in Fig. 7.

The critical output resistance  $(R_{crit})$  of the UGC converter is expressed in terms of switching frequency  $(f_s)$  and duty ratio (d) using (12), and it is obtained as

$$R_{crit} = \frac{2.f_s.L_3}{(1-d)^2.d} \tag{13}$$

### D. Parameter Design Converter

i. Inductor Design;- The value of the inductor is depends upon the switching frequency  $(f_s)$ , allowable maximum inductor current ripples, duty cycle (d), and the supply voltage  $(V_{in})$ . For best estimation, the ripple current  $\Delta i_L$  of the inductor should be chosen to be between 20% and 40% of the average inductor current. The selection of inductors for the UGC converter is based on the consideration of a maximum ripple current of 35% across the inductor.

$$\begin{cases}

L_{1} \geq \frac{d.V_{in}}{\Delta i_{L1}.f_{s}} \\

L_{2} \geq \frac{d.V_{in}}{\Delta i_{L2}.(1-d).f_{s}} \\

L_{3} \geq \frac{d.V_{in}}{\Delta i_{L3}.(1-d)^{2}.f_{s}}

\end{cases} (14)$$

ii. Capacitor Design:- The essential factor to consider when selecting capacitors is the acceptable voltage ripple. It is notable that the filter capacitor  $C_3$  and intermediate capacitors  $C_1$  &  $C_2$  have a maximum permitted voltage ripple of 1% and 2% of their average values, respectively. The specifications to choose a size of capacitor are as follows:

$$\begin{cases}

C_1 \ge \frac{d.i_0}{(1-d)^2.\Delta V_{C1}.f_s} \\

C_2 \ge \frac{d.i_0}{(1-d).\Delta V_{C2}.f_s} \\

C_3 \ge \frac{d.i_0}{\Delta V_{C3}.f_s}

\end{cases}$$

(15)

iii. Voltage stress and Current stress: - The voltage and current stresses of switch and diodes are obtained as

$$\frac{V_Q}{V_{in}} = \frac{1}{(1-d)^3}; I_Q = \frac{\sqrt{d} \cdot (d^2 + 3(1-d)) i_0}{(1+d(-3+3d+d^2))};$$

$$\frac{V_{D1}}{V_{in}} = \frac{-1}{(1-d)}; I_{D1} = \frac{i_0}{\sqrt{(1-2d+d^2)(1-d)^3}}$$

(16)

$$\frac{V_{D2}}{V_{in}} = \frac{-d}{(1+d(d-2))}; I_{D2} = \frac{\sqrt{d}i_0}{(1+d(-3+3d+d^2))};$$

$$\frac{V_{D3}}{V_{in}} = \frac{-d}{(1+d(-3+3d+d^2))}; I_{D3} = \frac{\sqrt{d} \cdot (2-d)i_0}{(1-d)^3}$$

(17)

$$\frac{V_{D4}}{V_{in}} = \frac{-1}{(1-2d+d^2)}; I_{D4} = \frac{i_0}{\sqrt{(1-d)^3}}$$

$$\frac{V_{D5}}{V_{in}} = \frac{-1}{(1+d^3+d(-3+3d))}; I_{D5} = \frac{i_0}{\sqrt{(1-d)}}$$

(18)

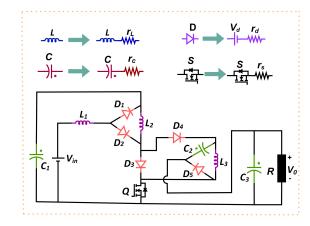

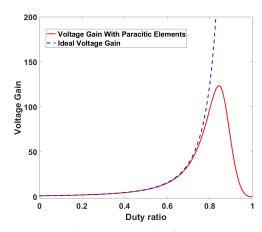

### E. UGC Converter with Non-idealities

The voltage gain obtained in (5) represents an ideal voltage gain when all parasitic elements are considered to be negligible. In practical scenario, parasitic elements may have the significant effect on the output voltage. The UGC converter with paracitic elements taken into consideration is as shown in Fig. 8 and the output voltage with Non-idealities presented in (24) & Fig. 9.

Fig. 8. UGC converter with non-idealties.

Fig. 9. Ideal and practical voltage gain of proposed UGC converter vs duty ratio plot.

# F. Small Signal Modelling of UGC Converter

By using state space average technique, the proposed nonlinear switching converter has to be converted to linearised model and it is perturbed around operating point to get constant duty.

The state space equations written by considering inductor currents  $i_{L01}, i_{L02}, i_{L03}$  and capacitor voltages  $u_{C01}, u_{C02}, u_{C03}$  as state variables. The input voltage is  $u_S(t)$ , while the voltage across the load resistance R is output  $u_0(t)$ . The converter is assumed to be operated in CCM.

In Continuous Conduction Mode (CCM), the converter operates in two modes: Mode-I, where the switch is turned ON, and Mode-II, when it is turned off. The converter's state can be represented by its state space matrices, as shown in (19)

and (20), as well as the corresponding state average matrix, which is illustrated in (21).

The load resistance R and duty ratio are specified as 352  $\Omega$  and 0.5804, respectively. The control to output voltage transfer function is obtained in (23).

$$TF = \frac{\widehat{v_o}(s)}{\widehat{d}}$$

$$TF = \frac{Z_5 s^5 + Z_4 s^4 + Z_3 s^3 + Z_2 s^2 + Z_1 s^1 + Z_0 s^0}{P_6 s^6 + P_5 s^5 + P_4 s^4 + P_3 s^3 + P_2 s^2 + P_1 s^1 + P_0 s^0}$$

(23)

As per the specifications provided in TABLE I, the poles

and zeros of the transfer function can be computed as follows:

$$P_{1,2}=(1.0e03)(-0.0003\pm4.5341i),\ P_{3,4}=(1.0e03)(-0.0005\pm2.8378i),\ P_{5,6}=(1.0e03)(-0.0103\pm0.1806i),\ Z_{1,2}=(1.0e04)(-0.0128\pm0.3536i),\ Z_3=(1.0e04)(-1.6867),\ Z_4=(1.0e04)(-0.1202),\ Z_5=(1.0e04)(0.0666)$$

The location of poles and zeros ensure that the proposed UGC is stable. Like conventional boost converter, the UGC converter also has one zero in right half plane, which indicates that UGC a stable but non minimum phase system.

$$\begin{bmatrix} \frac{di_{L_{01}}(t)}{dt} \\ \frac{dt}{dt_{02}}(t) \\ \frac{dt}{dt} \\ \frac{dt}{dt_{02}}(t) \\ \frac{dt}{dt} \\ \frac{dt}{dt_{02}}(t) \\ \frac{dt}{dt} \\ \frac{dt}{dt_{02}}(t) \\ \frac{dt}{dt} \\ \frac{dt}{$$

### III. EXPERIMENTAL RESULTS

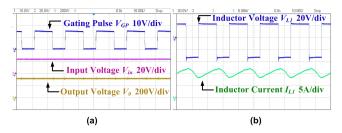

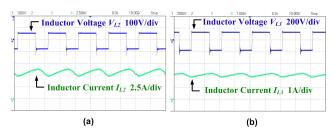

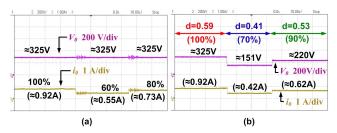

A 300-W laboratory hardware setup with a 325 V output and a 24 V input for the UGC converter has been constructed in accordance with the design displayed in Table I. The converter's Steady-State (SS) waveforms were recorded at  $V_{in}$ = 24 V and a duty cycle (d) of 0.59, resulting in an output voltage of 325 V which is shown in Fig. 10(a). The experimental waveforms of voltages across the inductors  $V_{L1}$ ,  $V_{L2}$  and  $V_{L3}$ , along with their corresponding currents  $i_{L1}$ ,  $i_{L2}$  and  $i_{L3}$  are displayed in Fig. 10(b) & Fig. 11.

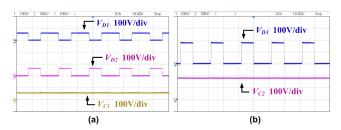

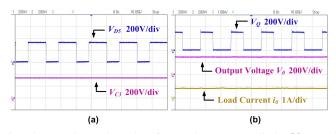

The voltage across each capacitor  $C_1$ ,  $C_2$  and  $C_3$  in Fig. 12 and Fig. 13(a) is 57.1 V, 187 V, and 324 V, respectively. The switching stresses for all diodes are as follows:  $V_{D1}$  is approximately 57.3 V,  $V_{D2}$  is approximately 71.2 V,  $V_{D3}$  is approximately 188 V,  $V_{D4}$  is approximately 136.2 V, and  $V_{D5}$  is approximately 324 V. These values may be found in Fig. 12 and Fig. 13(a). The experimental results in Fig.13

Fig. 10. Experimental results of (a) Gating pulse  $(V_{GP})$ , input voltage  $(V_{in})$  and output voltage  $(V_0)$  (b) Inductor voltage  $(V_{L1})$  and inductor current  $(I_{L1})$ .

show that the voltage stress between the switch Q and diode  $D_5$  is approximately 324 V. Fig. 14(a) illustrates that the load current changes from 100% to 60% and finally to 80% with respect to the desirable output voltage, whereas Fig. 14(b) displays a three-step variations in the duty ratio.

$$V_0 = \frac{V_S - (1 - d)V_{D1} - dV_{D2} - (2d - d^2)V_{D3} - (1 - d)^2V_{D4} - (1 - d)^5V_{D5}}{(1 - d)^3 + a\frac{1}{(1 - d)^3} + b\frac{1}{(1 - d)^2} + c\frac{1}{(1 - d)}}$$

(24)

$$a = \frac{1}{R} * \left\{ r_{L1} + (d^3 + 3(d - d^2) * r_S + (1 - d) * r_{D1} + d * r_{D2} + (2d - d^2) * r_{D3} \right\}$$

(25)

$$b = \frac{1}{R} * \left\{ (1 - d) * r_{L2} + (d^3 + 3d(1 - d)) * r_S + (2d - d^2) * r_{D3} + (1 - d)^2 * r_{D4} \right\}$$

(26)

$$c = \frac{1}{R} * \left\{ (1 + d^2 - 2d) * r_{L3} + (d^3 + 3d(1 - d)) * r_S + (1 - d)^3 * r_{D5} \right\}$$

(27)

Fig. 11. Experimental results of (a) Inductor voltage  $(V_{L2})$  and inductor current  $(I_{L2})$  (b) Inductor voltage  $(V_{L3})$  and inductor current  $(I_{L3})$ .

Fig. 12. Experimental results of (a) Voltage across diodes  $(V_{D1}, V_{D2})$  and capacitor voltage  $(V_{C1})$  (b) Voltage across diode  $(V_{D3})$  and capacitor voltage  $(V_{C2})$ .

Fig. 13. Experimental results of (a) Voltage across diode  $(V_{D5})$  and capacitor voltage  $(V_{C3})$  (b) Switch voltage stress  $(V_Q)$ , output voltage  $(V_0)$  and load current  $(i_0)$ .

The maximum achievable efficiency in the experiment is recorded as 94.1%.

### A. Performance Comparison of UGC Converter

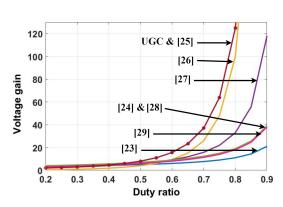

In order to verify the UGC converter superiority over recent converters, a comparison analysis was done and shown in Fig. 15. A comparison study of proposed ultra gain converter with the existing converters in terms of output voltage gain, number of semi conductor devices, and number of storage elements and total count is presented in Table II. The UGC

Fig. 14. (a) Dynamic variation of load current  $(i_0)$  when the load changes from 352  $\Omega$  to 586  $\Omega$ , and then to 440  $\Omega$  (b) Dynamic variation of output voltage  $(V_0)$  and load current  $(i_0)$  when duty ratio changes from 100% to 70%, and then to 90%.

# TABLE I SPECIFICATIONS OF UGC CONVERTER

| Input Voltage $V_{in}$               | 24 V                         |

|--------------------------------------|------------------------------|

| Rated Power $P_{out}$                | 300 W                        |

| $L_1, L_2, L_3$                      | 0.33 mH, 0.42 mH and 0.72 mH |

| Switching frequency $f_s$            | 50 kHz                       |

| $C_1, C_2, C_3$                      | 22 uF, 47 uF, 110 uF         |

| Mosfet $Q$                           | IRFP460                      |

| Power diodes $D_1, D_2$              | MUR820                       |

| Power diodes $D_3$ , $D_4$ and $D_5$ | MUR860                       |

| Output Voltage $V_0$                 | 325 V                        |

converter has one switch and five diodes, while the reported converters [23], [26], [27], [28], and [29] also contain one switch. However, the use of fourteen diodes in [24], seven diodes in [28], and six diodes in [29]. There are more number inductors and capacitors utilized in [24]. Compared to the UGC, the converters reported in [24], [27], and [28] use higher number of components and achieve lower voltage gain. The converter stated in [25] have the same voltage gain as the UGC, but requires three switches. In contrast to the converters described in [23], [24], [26], [28], and [29], the proposed converter provides a common ground feature.

Table III highlights the various converter losses associated with the inductor, switch, and snubber. Table III is formulated using the following values: L= 100 uH,  $C_s$ = 4.7 uF,  $f_s$ = 50 kHz, and  $i_0$ = 1A. For a 325 V output voltage, the duty ratios of the several converters were calculated. The UGC converter's duty ratio was 0.5804, while the ones reported in [26], [27], and [29] were 0.64, 0.67, and 0.74 respectively. In terms of performance comparison, the UGC converter has less losses than the ones reported in [26], [27] and [29].

| Topology         | [23]                | [24]                | [25]                | [26]                | [27]                        | [28]                | [29]                 | Proposed UGC        |

|------------------|---------------------|---------------------|---------------------|---------------------|-----------------------------|---------------------|----------------------|---------------------|

| switches         | 1                   | 6                   | 3                   | 1                   | 1                           | 1                   | 1                    | 1                   |

| Diodes           | 4                   | 14                  | 3                   | 3                   | 5                           | 7                   | 6                    | 5                   |

| Inductors        | 1                   | 6                   | 3                   | 3                   | 4                           | 2                   | 2                    | 3                   |

| Capacitors       | 4                   | 8                   | 3                   | 5                   | 6                           | 4                   | 3                    | 3                   |

| Total count      | 10                  | 34                  | 12                  | 12                  | 16                          | 14                  | 12                   | 12                  |

| Voltage Gain     | $\frac{3-d}{(1-d)}$ | $\frac{3+d}{(1-d)}$ | $\frac{1}{(1-d)^3}$ | $\frac{d}{(1-d)^3}$ | $\frac{1+2d-2d^2}{(1-d)^2}$ | $\frac{3+d}{(1-d)}$ | $\frac{2+2d}{(1-d)}$ | $\frac{1}{(1-d)^3}$ |

| CCM Gain d @ 0.8 | 11                  | 19                  | 125                 | 100                 | 33                          | 19                  | 18                   | 125                 |

| Common Ground    | No                  | No                  | Yes                 | No                  | Yes                         | No                  | No                   | Yes                 |

TABLE II

COMPARATIVE ANALYSIS OF UGC CONVERTER WITH EXISTING TOPOLOGIES

TABLE III

PERFORMANCE WISE COMPARISON OF UGC CONVERTER

| References                     | [26], 2023                                                   | [27], 2023                                                                                                                            | [29], 2021                                                                            | Proposed UGC                                                                        |

|--------------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Dutyratio Required             | V <sub>in</sub> =24 V<br>d=0.63869                           | $V_{in}$ =24 V d=0.62914                                                                                                              | V <sub>in</sub> =24 V<br>d=0.7426                                                     | V <sub>in</sub> =24 V<br>d=0.5804                                                   |

| Output voltage                 | $24 \cdot \frac{d}{(1-d)^3}$ =325 V                          | $24 \cdot \frac{1+2d-d^2}{(1-d)^2} = 325V$                                                                                            | $24 \cdot \frac{2+2d}{(1-d)}$ $=325V$                                                 | $24 \cdot \frac{1}{(1-d)^3}$ $=325V$                                                |

| Current through inductor $L_1$ | $\frac{V_s}{L} \cdot dT_s$ $= 3.065A$                        | $\frac{V_s}{L} \cdot dT_s$ = 3.015A                                                                                                   | $\frac{V_s}{L} \cdot dT_s$ $= 3.565A$                                                 | 7 705 4                                                                             |

| Inductor Loss $L_1$            | $\frac{(d.i_o)^2}{(1-d)^6} \cdot r_L$ =183.35 $\cdot r_L$    | $i_{o} \begin{bmatrix} 8d - 4d^{2} - \\ \left(\frac{1}{d-1}\right) + \\ \left(\frac{1}{(d-1)^{2}}\right) + 1 \end{bmatrix}^{2}$       | $\begin{array}{l} \frac{(4.i_o)^2}{(1-d)^2} \cdot r_L \\ = 241 \cdot r_L \end{array}$ | $\begin{array}{l} \frac{(i_o)^2}{(1-d)^6} \cdot r_L \\ = 183 \cdot r_L \end{array}$ |

| Switch conduction Losses       | $\frac{d{i_o}^2}{(1-d)^6} \cdot r_{ds}$ = 117 $\cdot r_{ds}$ | $= 206.01 \times r_L$ $i_o^2 d^2 \begin{bmatrix} 6d - 8d^2 + \\ (d-2)(2d-3) \\ (d-1)^2 \end{bmatrix}^2 r_{ds}$ $= 127.7 \cdot r_{ds}$ | $\frac{\frac{16di_0^2}{(1-d)^2}r_{ds}}{=179 \cdot r_{ds}}$                            | $\left(\frac{i_0}{(1-d)^3}\right)^2 dr_L$ = 106 · $r_{ds}$                          |

Fig. 15. Comparative DC voltage gain of UGC converter with existing topologies.

# IV. CONCLUSION

In this paper, a novel UGC converter is proposed. The proposed converter was explained in CCM and DCM and condition for BCM also derived. A comparison with the latest literature converters highlights the benefits of the UGC converter further. The UGC converter was developed to have an output power of 300 W and an output voltage of 325 V. However, the voltage stress across the switch Q and diode  $D_5$  is the same to that of the output voltage, which is a disadvantage. The experimental results validate that high voltage gain was obtained without using VM, coupled circuits and/or transformers. The UGC converter is an excellent choice for many applications such as Electric Vehicles, Smart lighting, Medical devices, Military applications, Renewable energy integration etc.

# V. APPENDIX A

# A. Calculation of Ideal Voltage Gain in CCM

The volt-sec balance relation for inductor  $L_1$  is

$$V_{L1}(dT) + V_{L1}(1-d)T = 0 (28)$$

from (1) & (3)

Voltage across inductor  $L_1$  during switch ON (dT) period is  $V_{in}$  and voltage across inductor  $L_1$  during switch OFF ((1-d)T) period is  $(V_{in}$ - $V_{C1}$ ). By substituting these values in (28), gives

$$V_{in}(dT) + (V_{in} - V_{C1})(1 - d)T = 0$$

(29)

by simplifying (29),

$$V_{C1} = \frac{V_{in}}{(1-d)} \tag{30}$$

similarly, the volt-sec balance relation for inductor  $L_2$  &  $L_3$  (using (1) & (3)) are obtained as follows

$$V_{C1}(dT) + (V_{C1} + V_{C2} - V_0)(1 - d)T = 0 (31)$$

$$(V_0 - V_{C2})(dT) + (-V_{C2})(1 - d)T = 0 (32)$$

simplifying (32), yields

$$V_0.d = V_{C2} (33)$$

Substituting (30) and (33) into (31) gives the ideal voltage gain  $G_{VCCM}$  of the UGC converter in CCM.

$$G_{VCCM} = \frac{V_0}{V_{in}} = \frac{1}{(1-d)^3}$$

(34)

# B. Calculation of Ideal Current Gain in CCM

The ideal current gain can be calculated by using charge-sec balance relation or using power balance relation. In an ideal converter, input power and output power are equal, which is written as

$$V_{in}.i_{in} = V_0.i_0 (35)$$

rewriting (35) as

$$\frac{i_0}{i_{in}} = \frac{V_{in}}{V_0} \tag{36}$$

The ideal current gain  $G_{ICCM}$  of the UGC converter in CCM is obtained by using (34) in (36)

$$G_{ICCM} = \frac{i_0}{i_{in}} = (1 - d)^3 \tag{37}$$

# VI. APPENDIX B

### A. Inductor Design

During Mode-I, the voltage across inductor  $L_1$  is

$$V_{L1} = L_1 \frac{di_{L_1}}{dt} = V_{in} (38)$$

i.e.,

$$V_{L1} = L_1 \frac{\Delta i_{L_1}}{dT} = V_{in} \tag{39}$$

Therefore, The inductor  $L_1$  value is computed as

$$L_1 = \frac{V_{in} \cdot d}{\Delta i_{L_1} \cdot f_s} \tag{40}$$

similarly, the inductor values  $L_2$  and  $L_3$  are written as

$$L_2 = \frac{V_{L2}}{\Delta i_{L_2}} dT = \frac{V_{C1}}{\Delta i_{L_2}} dT = \frac{d.V_{in}}{\Delta i_{L_2}.(1-d).f_s}$$

(41)

$$L_3 = \frac{V_{L3}}{\Delta i_{L_3}} dT = \frac{(V_0 - V_{C2})dT}{\Delta i_{L_3}} = \frac{d \cdot V_{in}}{\Delta i_{L_3} \cdot (1 - d)^2 \cdot f_s}$$

(42)

# B. Capacitor Design

During Mode-I, the current through capacitor  $C_1$  is

$$i_{C1(ON)} = C_1 \frac{dV_{C_1}}{dt} = i_{L2}$$

(43)

i.e.,

$$i_{C1(ON)} = C_1 \frac{\Delta V_{C_1}}{dT} = i_{L2}$$

(44)

Therefore, the value of capacitor  $C_1$  is calculated as

$$C_1 = \frac{i_{L2}}{\Delta V_{C_1}} dT = \frac{d.i_0}{(1-d)^2 . \Delta V_{C_1} . f_s}$$

(45)

similarly, the values of capacitors  $C_2$  and  $C_3$  are obtained as

$$C_2 = \frac{i_{L3}}{\Delta V_{C_2}} dT = \frac{d.i_0}{(1-d).\Delta V_{C2}.f_s}$$

(46)

$$C_3 = \frac{i_0}{\Delta V_{C_3}} dT = \frac{d.i_0}{\Delta V_{C_3}.f_s} \tag{47}$$

# C. Diode Voltage Stress

During CCM Mode-I, diodes  $D_1$ ,  $D_4$  and  $D_5$  are not conducting. By applying KVL to Mode-I circuit, the following equations were obtained.

$$V_{D1} = V_{in} - V_{L1} - V_{C1} (48)$$

$$V_{D5} = -V_{C2} - V_{L3} (49)$$

$$V_{D4} = V_{in} - V_{L1} + V_{C2} - V_0 (50)$$

Using (1), (30) and (33) to solve (48), (49), and (50) yields

$$V_{D1} = \frac{-V_{in}}{(1-d)} \tag{51}$$

$$V_{D4} = \frac{-V_{in}}{(1 - 2d + d^2)} \tag{51}$$

$$V_{D5} = \frac{-V_{in}}{(1+d^3+d(-3+3d))}$$

(52)

Similarly, during CCM Mode II, the following KVL equations were obtained for the diodes  $D_2$ ,  $D_3$ .

$$V_{D2} = V_{in} - V_{L1} + V_{C2} - V_0 (53)$$

$$V_{D3} = -V_{L3} (54)$$

Using (3), (30) and (33) to solve (53) and (54) gives,

$$V_{D2} = \frac{-V_{in}.d}{(1+d(d-2))}$$

(55)

$$V_{D3} = \frac{-V_{in}.d}{(1+d(-3+3d+d^2))}$$

(56)

### REFERENCES

- [1] B. Zeng, J. Zhang, X. Yang, J. Wang, J. Dong and Y. Zhang, "Integrated Planning for Transition to Low-Carbon Distribution System With Renewable Energy Generation and Demand Response," in IEEE Transactions on Power Systems, vol. 29, no. 3, pp. 1153-1165, 2014, doi: 10.1109/TPWRS.2013.2291553.

- [2] F. Blaabjerg, R. Teodorescu, M. Liserre and A. V. Timbus, "Overview of Control and Grid Synchronization for Distributed Power Generation Systems," in IEEE Transactions on Industrial Electronics, vol. 53, no. 5, pp. 1398-1409, 2006, doi: 10.1109/TIE.2006.881997.

- [3] M. S. Bhaskar, D. J. Almakhles, S. Padmanaban, F. Blaabjerg, U. Subramaniam and D. M. Ionel, "Analysis and Investigation of Hybrid DC–DC Non-Isolated and Non-Inverting Nx Interleaved Multilevel Boost Converter (Nx-IMBC) for High Voltage Step-Up Applications: Hardware Implementation," in IEEE Access, vol. 8, pp. 87309-87328, 2020, doi: 10.1109/ACCESS.2020.2992447.

- [4] B. P. R. Baddipadiga, V. A. K. Prabhala and M. Ferdowsi, "A Family of High-Voltage-Gain DC–DC Converters Based on a Generalized Structure," in IEEE Transactions on Power Electronics, vol. 33, no. 10, pp. 8399-8411, 2018, doi: 10.1109/TPEL.2017.2777451.

- [5] alilzadeh T, Rostami N, Babaei E, Maalandish M., "Ultra-step-up dc-dc converter with low-voltage stress on devices" in IET Power Electrons, Volume 12, pp. 345-357, 2019, 10.1049/iet-pel.2018.53565.

- [6] Hema Rani, Manikanta K., Saly George, Ashok. "Power Management Using One Cycle Control Strategy for Triple Input Single Output Fly Back DC–DC Converter" in Electric Power Components and Systems, vol. 50, pp. 600–614, 2022, doi: 10.1080/15325008.2022.2138639.

- [7] V. R. K. Kanamarlapudi, B. Wang, N. K. Kandasamy and P. L. So, "A New ZVS Full-Bridge DC–DC Converter for Battery Charging With Reduced Losses Over Full-Load Range," in IEEE Transactions on Industry Applications, vol. 54, no. 1, pp. 571-579, 2018, 10.1109/TIA.2017.2756031.

- [8] F. I. Kravetz and R. Gules, "Soft-Switching High Static Gain Modified SEPIC Converter," in IEEE Journal of Emerging and Selected Topics in Power Electronics, vol. 9, no. 6, pp. 6739-6747, 2021, 10.1109/JESTPE.2021.3079573.

- [9] L. Qin, L. Zhou, W. Hassan, J. L. Soon, M. Tian and J. Shen, "A Family of Transformer-Less Single-Switch Dual-Inductor High Voltage Gain Boost Converters With Reduced Voltage and Current Stresses," in IEEE Transactions on Power Electronics, vol. 36, no. 5, pp. 5674-5685, 2021, 10.1109/TPEL.2020.3032549.

- [10] S. Sadaf, M. S. Bhaskar, M. Meraj, A. Iqbal and N. Al-Emadi, "Transformer-Less Boost Converter With Reduced Voltage Stress for High Voltage Step-Up Applications," in IEEE Transactions on Industrial Electronics, vol. 69, no. 2, pp. 1498-1508, 2022, 10.1109/TIE.2021.3055166.

- [11] S. Selvam, M. Sannasy and M. Sridharan, "Analysis and Design of Two-Switch Enhanced Gain SEPIC Converter," in IEEE Transactions on Industry Applications, vol. 59, no. 3, pp. 3552-3561, 2023, 10.1109/TIA.2023.3242237.

- [12] V. Karthikeyan, S. Kumaravel and G. Gurukumar, "High Step-Up Gain DC-DC Converter With Switched Capacitor and Regenerative Boost Configuration for Solar PV Applications," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 66, no. 12, pp. 2022-2026, 2019, 10.1109/TCSII.2019.2892144

- [13] R. Stala et al., "High-Gain Switched-Capacitor DC-DC Converter With Low Count of Switches and Low Voltage Stress of Switches," in IEEE Access, vol. 9, pp. 114267-114281, 2021, 10.1109/ACCESS.2021.3104399.

- [14] Izadi, M., Mosallanejad, A., Eshkevari, A.L.: An improved coupled inductor-based quadratic step-up DC–DC converter with a high step-up factor and reduced voltage overshoot on the power switch," in IET Power Electron. vol. 17, pp. 986-1004, 2023, 10.1049/pel2.12567.

- [15] Maalandish, M., Babaei, E., Abolhasani, P., Gheisarnejad, M., Khooban, M.-H. "Ultra high step-up soft-switching DC/DC converter using coupled inductor and interleaved technique," in IET Power Electron. vol. 16, pp. 1320–1338, 2023, 10.1049/pel2.12472.

- [16] Hwu, K.-I., Shieh, J.-J. and Jiang, W.-Z, "Three-level boost converter with zero voltage transition," The Journal of Engineering, vol. 2017, pp. 354-361, 2017, 10.1049/joe.2017.0149.

- [17] B. Zhu, G. Liu, Y. Zhang, Y. Huang and S. Hu, "Single-Switch High Step-Up Zeta Converter Based on Coat Circuit," in IEEE Access, vol. 9, pp. 5166-5176, 2021, 10.1109/ACCESS.2020.3048388.

- [18] A. Alzahrani, M. Ferdowsi and P. Shamsi, "A Family of Scalable Non-Isolated Interleaved DC-DC Boost Converters With Voltage Multiplier Cells," in IEEE Access, vol. 7, pp. 11707-11721, 2019, 10.1109/AC-CESS.2019.2891625.

- [19] V. Seshagiri Rao and K. Sundaramoorthy, "Performance Analysis of Voltage Multiplier Coupled Cascaded Boost Converter With Solar PV Integration for DC Microgrid Application," in IEEE Transactions on Industry Applications, vol. 59, no. 1, pp. 1013-1023, 2023, 10.1109/TIA.2022.3209616.

- [20] S. Khan et al., "A New Transformerless Ultra High Gain DC–DC Converter for DC Microgrid Application," in IEEE Access, vol. 9, pp. 124560-124582, 2021, 10.1109/ACCESS.2021.3110668.

- [21] N. Zhang, G. Zhang, K. W. See and B. Zhang, "A Single-Switch Quadratic Buck–Boost Converter With Continuous Input Port Current and Continuous Output Port Current," in IEEE Transactions on Power Electronics, vol. 33, no. 5, pp. 4157-4166, 2018, 10.1109/TPEL.2017.2717462.

- [22] Mizani A, Ansari SA, Shoulaie A, Davidson JN, Foster MP. "Single-active switch high-voltage gain DC–DC converter using a non-coupled inductor," in IET Power Electron, vol. 14, pp. 492–502, 2021, 10.1049/pel2.12007.

- [23] F. Mohammadi, G. B. Gharehpetian, H. Rastegar and M. Farhadi-Kangarlu, "Non-isolated Step-up DC-DC Converter Based on Switched Capacitor Cells," in CSEE Journal of Power and Energy Systems, vol. 9, no. 3, pp. 1161-1172, 2023, 10.17775/CSEEJPES.2021.07370.

- [24] Maalandish, M., Hosseini, S.H., Ghasemzadeh, S., Babaei, E., Shalchi Alishah, R. and Jalilzadeh, T., Six-phase interleaved boost dc/dc converter with high-voltage gain and reduced voltage stress," in IET Power Electronics, vol. 10, pp. 1904-1914, 2017, 10.1049/iet-pel.2016.1029.

- [25] Z. Saadatizadeh, P. C. Heris, M. Sabahi and E. Babaei, "A DC–DC Transformerless High Voltage Gain Converter With Low Voltage Stresses on Switches and Diodes," in IEEE Transactions on Power Electronics, vol. 34, no. 11, pp. 10600-10609, 2019, 10.1109/TPEL.2019.2900212.

- [26] M. A. B. Kumar and V. Krishnasamy, "A Single-Switch Continuous Input Current Buck–Boost Converter With Noninverted Output Voltage," in IEEE Transactions on Power Electronics, vol. 38, no. 2, pp. 2181-2190, 2023, 10.1109/TPEL.2022.3215179.

- [27] R. Rajesh, N. Prabaharan and T. K. Santhosh, "Design and Analysis of a Non-Isolated DC-DC Converter With a High-Voltage Conversion Ratio," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 70, no. 6, pp. 2036-2041, 2023, 10.1109/TCSII.2022.3226187.

- [28] S. Pirpoor, S. Rahimpour, M. Andi, N. Kanagaraj, S. Pirouzi and A. H. Mohammed, "A Novel and High-Gain Switched-Capacitor and Switched-Inductor-Based DC/DC Boost Converter With Low Input Current Ripple and Mitigated Voltage Stresses," in IEEE Access, vol. 10, pp. 32782-32802, 2022, 10.1109/ACCESS.2022.3161576.

- [29] T. Shanthi, S. U. Prabha and K. Sundaramoorthy, "Non-Isolated n-Stage High Step-up DC-DC Converter for Low Voltage DC Source Integration," in IEEE Transactions on Energy Conversion, vol. 36, no. 3, pp. 1625-1634, 2021, 10.1109/TEC.2021.3050421.

Kuraganti Manikanta received a B.Tech. degree in Electrical and Electronics Engineering from Sriprakash College of Engineering, JNTU-Kakinada, in 2014, and an M.Tech degree in Power Electronics from NIT-Calicut in 2019. He is presently pursuing a Ph.D. in high gain dc-dc converters at the National Institute of Technology Warangal, India. His area of interest includes High-gain DC-DC converters, Multi-input single-output converters, and Electric Vehicles.

Ramulu Chinthamalla (Senior Member, IEEE) received the B.Tech. degree from the Gokaraju Rangaraju Institute of Engineering and Technology (GRIET), Jawaharlal Nehru Technological University, Hyderabad, Telangana, India, in 2001, and the M.Tech. degree in power electronics and drives and the Ph.D. degree in electrical engineering from the National Institute of Technology Warangal, Warangal, India, in 2005 and 2017, respectively. Since 2012, he has been an Assistant Professor with the Department of Electrical Engineering, National In-

stitute of Technology Warangal. His research interests include power electronics and drives, application of power electronics to nonconventional energy conditioning, AC-DC electrolytic capacitorless single-phase LED drivers, and high-gain DC-DC converters.